# **XSCHEM : schematic capture and netlisting EDA tool**

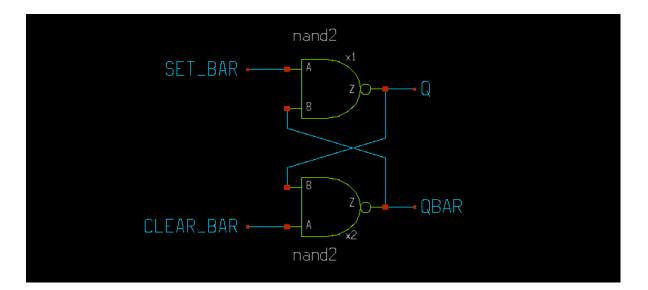

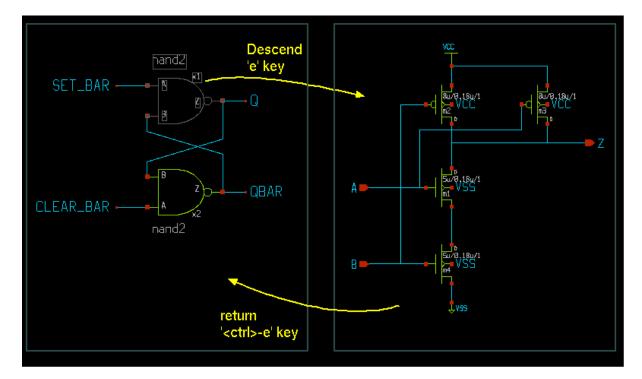

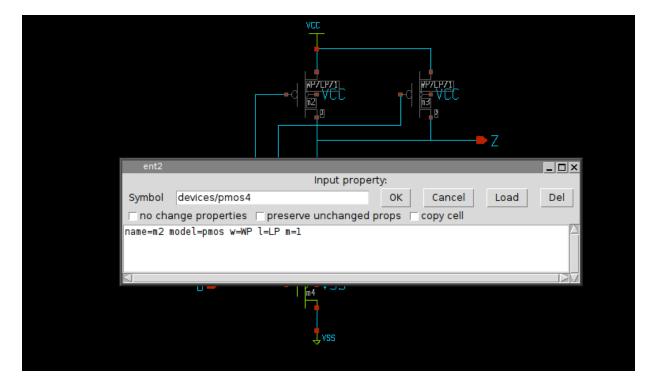

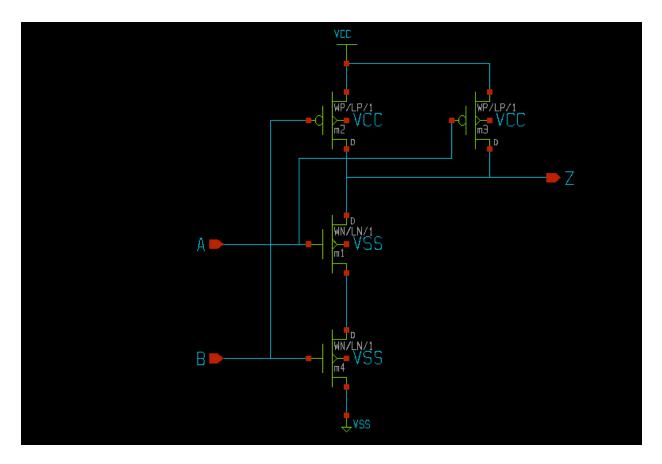

**Xschem** is a schematic capture program, it allows creation of hierarchical representation of circuits with a top down approach. By focusing on interfaces, hierarchy and instance properties a complex system can be described in terms of simpler building blocks. A VHDL or Verilog or Spice netlist can be generated from the drawn schematic, allowing the simulation of the circuit. Key feature of the program is its drawing engine written in C and using directly the Xlib drawing primitives; this gives very good speed performance, even on very big circuits. The user interface is built with the Tcl-Tk toolkit, tcl is also the extension language used.

## Features

- hierarchical schematic drawings, no limits on size

- any object in the schematic can have any sort of properties (generics in VHDL, parameters in Spice or Verilog)

- new Spice/Verilog primitives can be created, and the netlist format can be defined by the user

- tcl extension language allows the creation of scripts; any user command in the drawing window has an associated tcl comand

- VHDL / Verilog / Spice netlist, ready for simulation

- Behavioral VHDL / Verilog code can be embedded as one of the properties of the schematic block,

Xschem runs on UNIX systems with X11 and Tcl-Tk toolkit installed.

## Documentation

### XSCHEM manual

## Download

<u>Current release</u> <u>Old XSCHEM releases on Sourceforge</u> SVN: svn checkout svn://repo.hu/xschem/trunk

## License

The software is released under the GNU GPL, General Public License

## Contact

Anyone interested in this project please contact me at the following address:

#### STEFAN.SCHIPPERS@GMAIL.COM

## Software requirements:

- X11

- tcl-tk libs and developent files

- c99 compiler

- bison (only for compiling the grammar parser)

- flex (only for compiling the lexical analyzer

- Xpm library and -dev header files

- awk (tested with gawk and mawk)

## Systems tested:

- Linux debian / Redhat

- Solaris sparc

- Windows (with the cygwin layer and cygwin/Xorg X11 server, plus the tcl/tk toolkit and the - dev libraries)

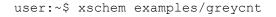

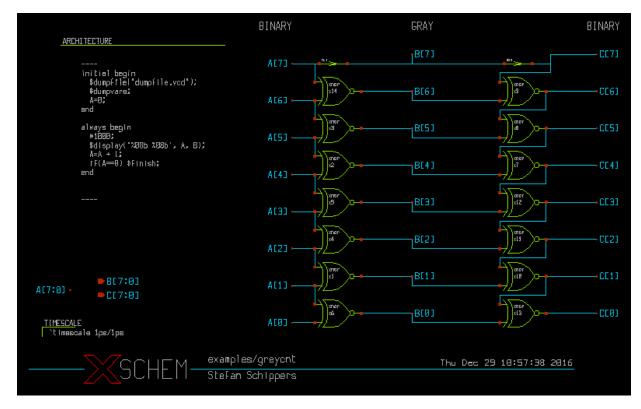

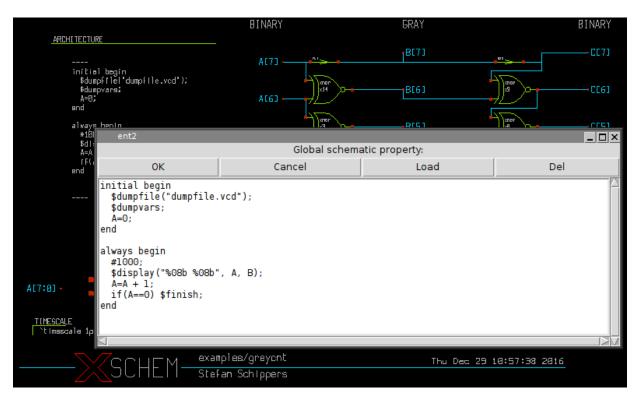

## **Screenshots**

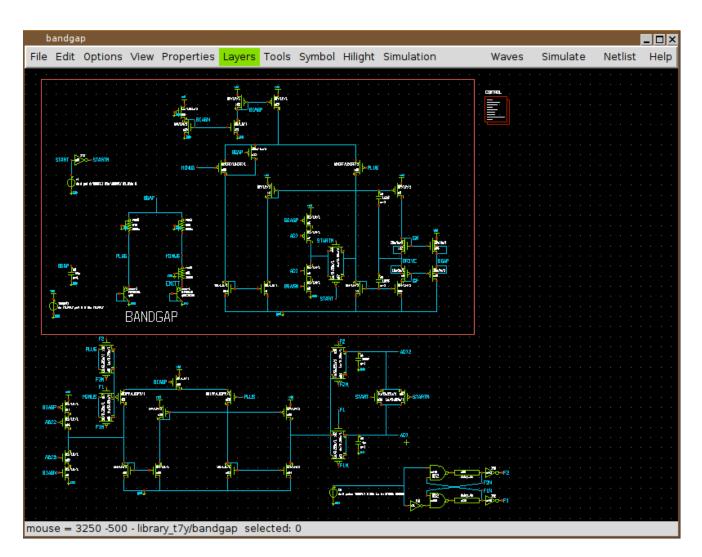

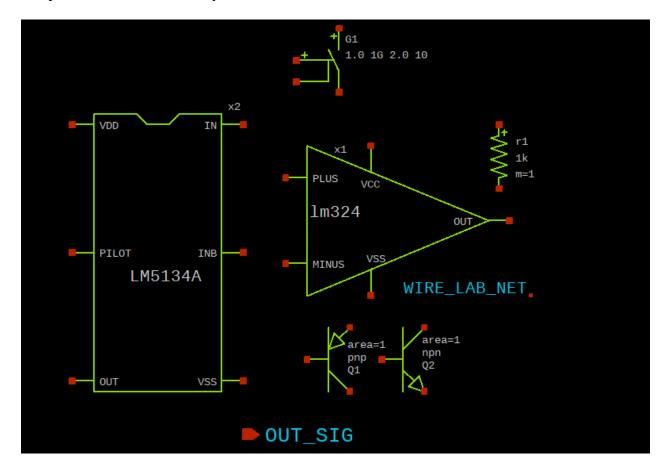

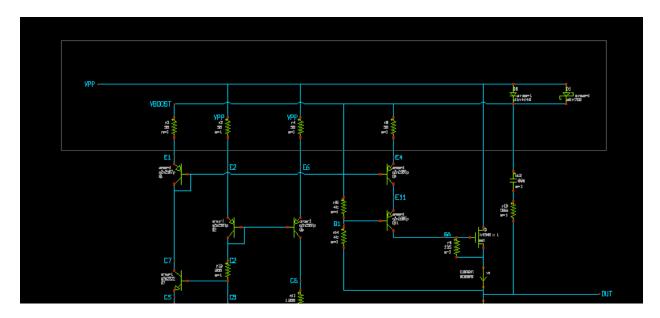

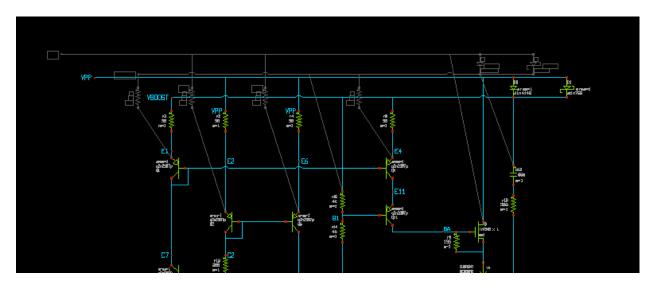

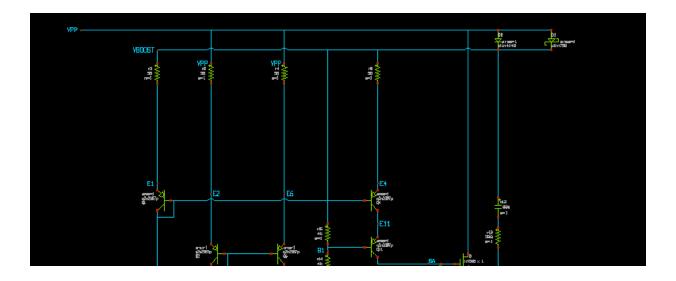

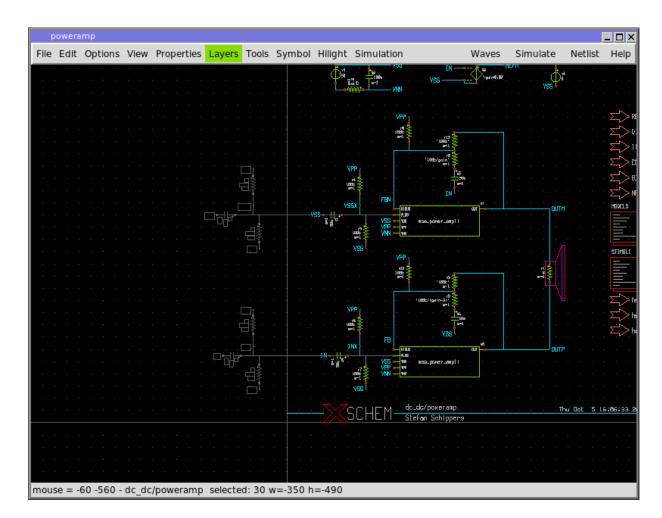

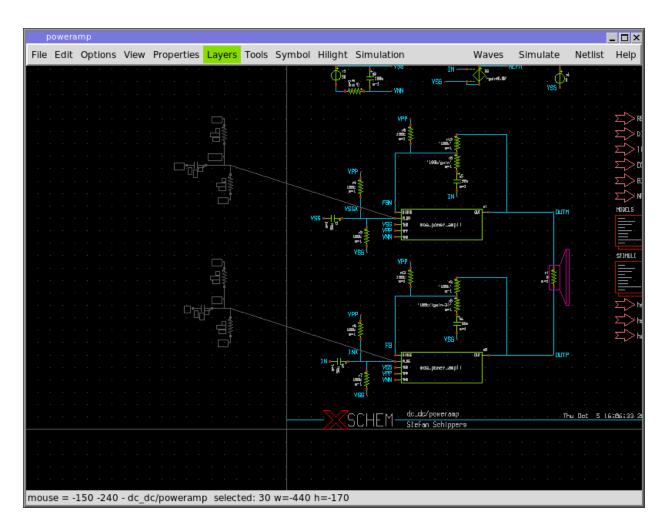

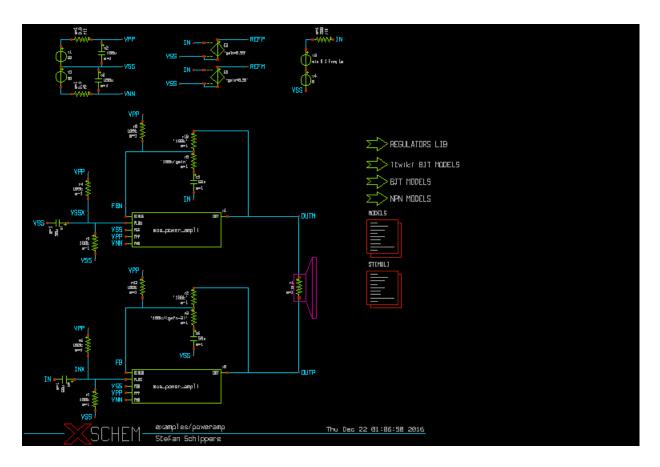

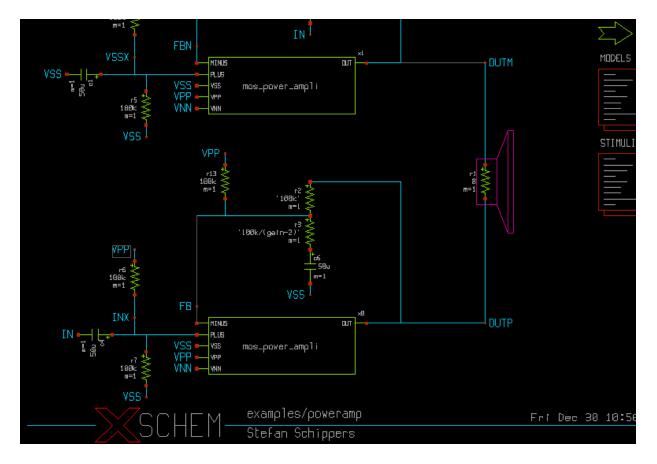

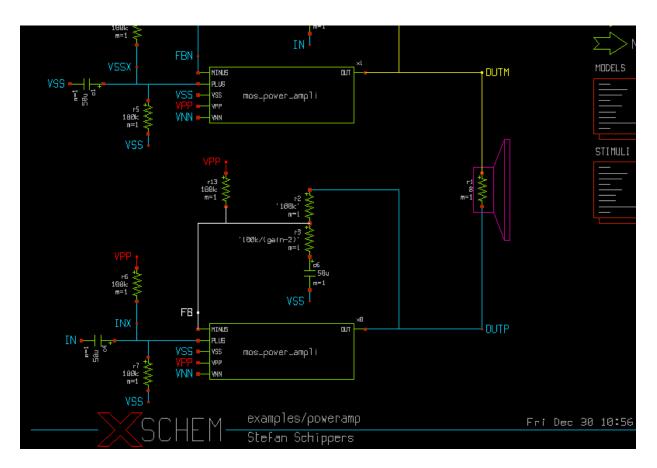

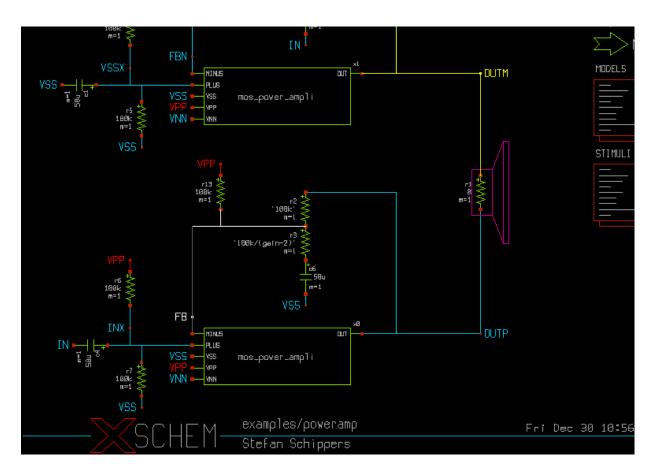

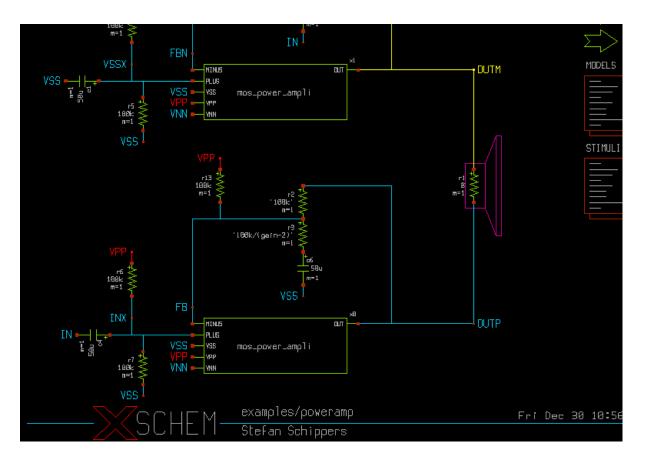

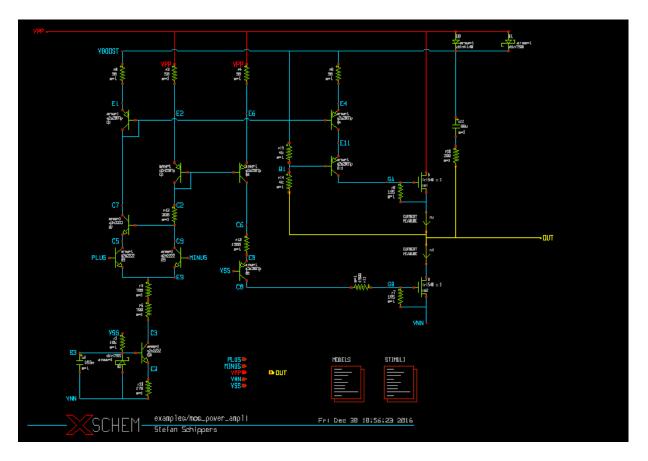

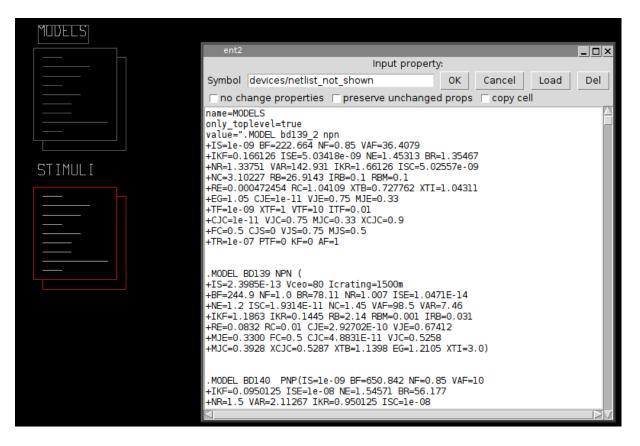

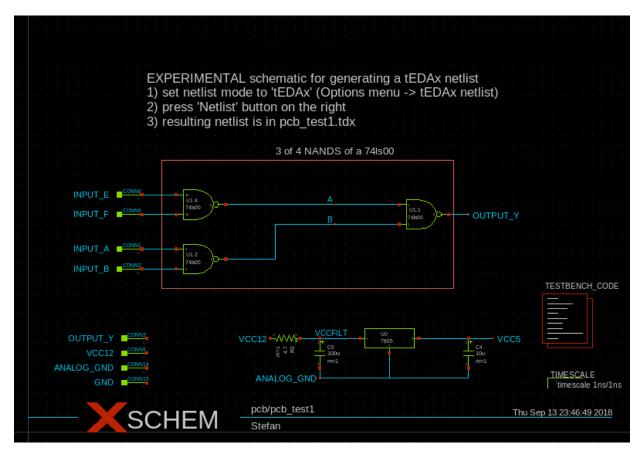

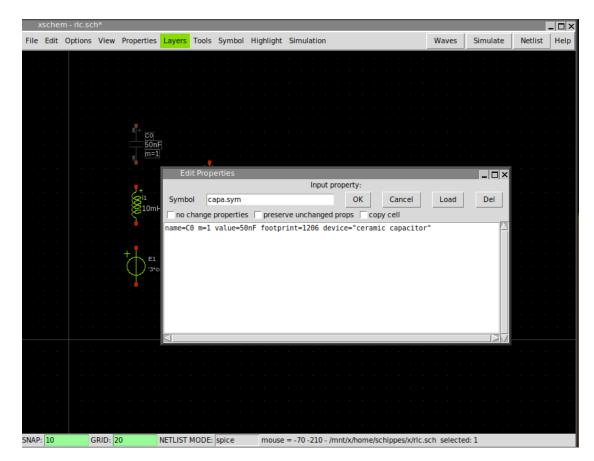

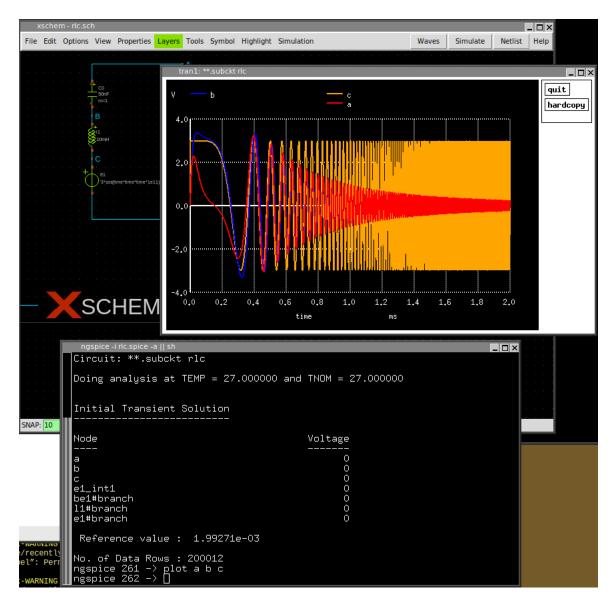

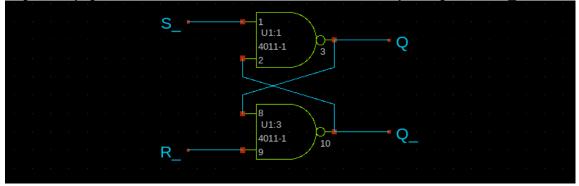

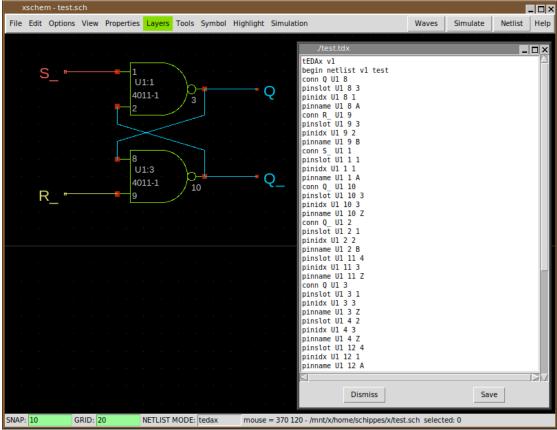

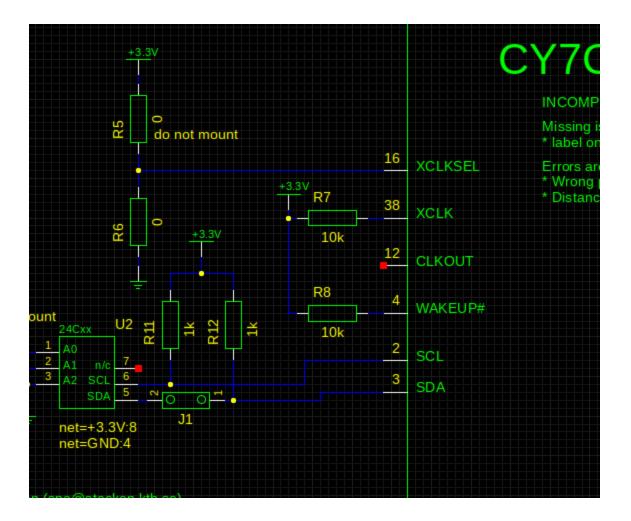

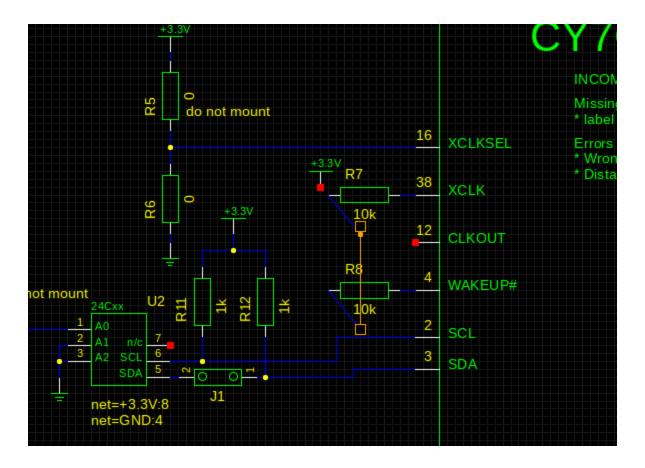

• analog circuit example

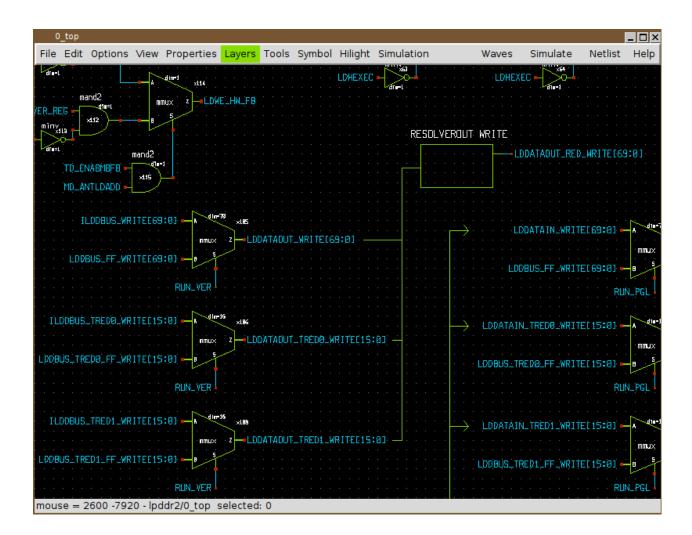

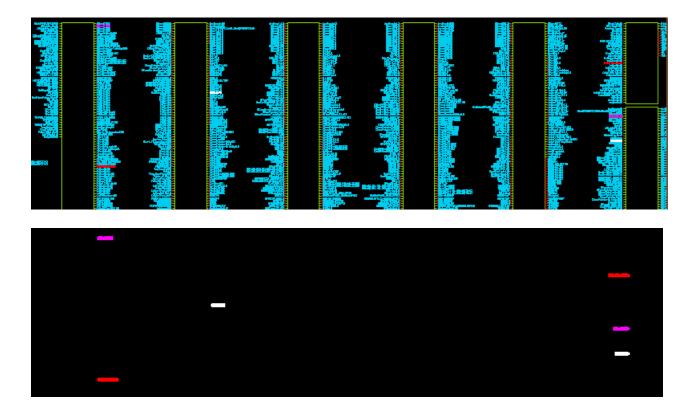

• digital system for VHDL simulation

## Contents

| XSCHEM : schematic capture and netlisting EDA tool | 1  |

|----------------------------------------------------|----|

| Features                                           | 1  |

| Documentation                                      | 1  |

| Download                                           | 1  |

| License                                            | 1  |

| Contact                                            | 2  |

| Software requirements:                             | 2  |

| Systems tested:                                    | 2  |

| Screenshots                                        | 2  |

| INDEX                                              | 8  |

| TUTORIALS                                          | 8  |

| FAQ                                                | 8  |

| WHAT IS XSCHEM                                     |    |

| INSTALL XSCHEM                                     | 13 |

| Detailed XSCHEM startup sequence                   | 14 |

| RUN XSCHEM                                         | 15 |

| XSCHEM COMMAND LINE OPTIONS                        | 16 |

| CREATING A NEW SCHEMATIC                           | 17 |

| XSCHEM ELEMENTS                                    | 20 |

| WIRES                                              | 20 |

| LINES                                              | 20 |

| RECTANGLES                                         | 21 |

| POLYGONS                                           | 22 |

| CIRCLES / ARCS                                     | 23 |

| ТЕХТ                                               | 23 |

| SYMBOLS                                            | 26 |

| XSCHEM PROPERTIES                                  |    |

| GLOBAL PROPERTIES                                  |    |

| PIN ORDERING                                       |    |

| COMPONENT INSTANTIATION                            |    |

| SPECIAL COMPONENTS                                 | 45 |

| SYMBOL PROPERTY SYNTAX                              | 47 |

|-----------------------------------------------------|----|

| GENERAL RULES                                       | 47 |

| ATTRIBUTE SUBSTITUTION                              |    |

| OTHER PREDEFINED SYMBOL ATTRIBUTES                  | 49 |

| PREDEFINED SYMBOL VALUES                            | 55 |

| COMPONENT PROPERTY SYNTAX                           | 57 |

| PREDEFINED COMPONENT ATTRIBUTES                     | 58 |

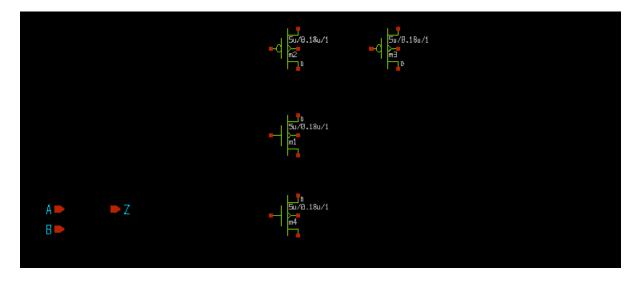

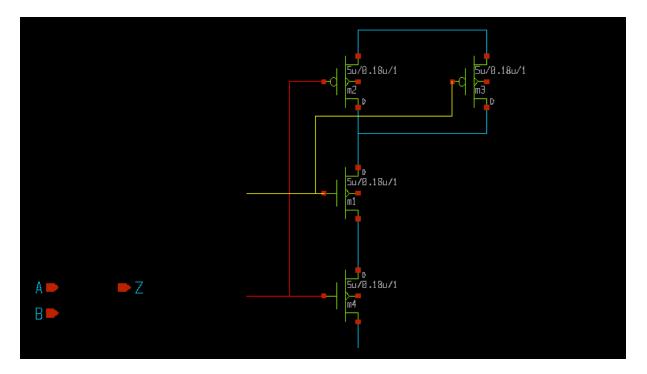

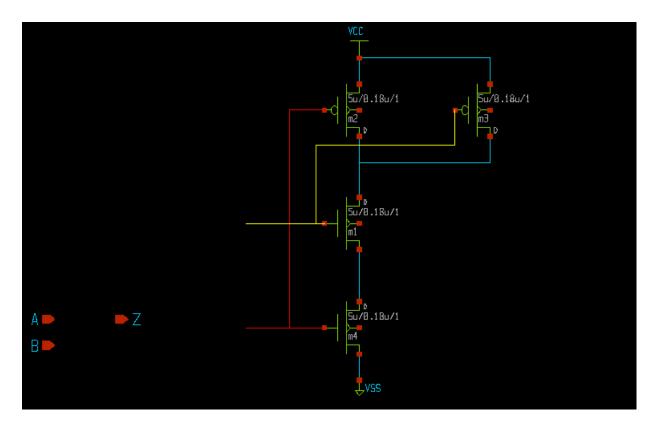

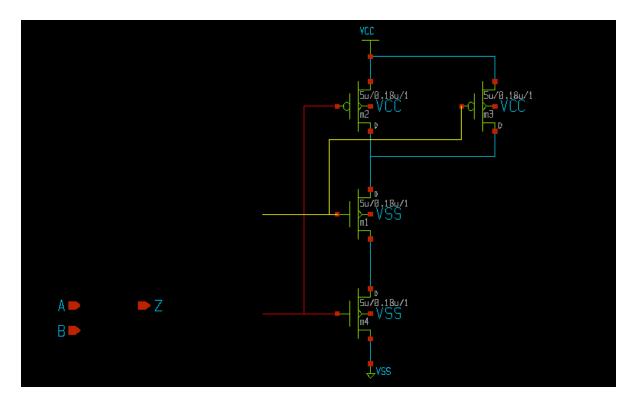

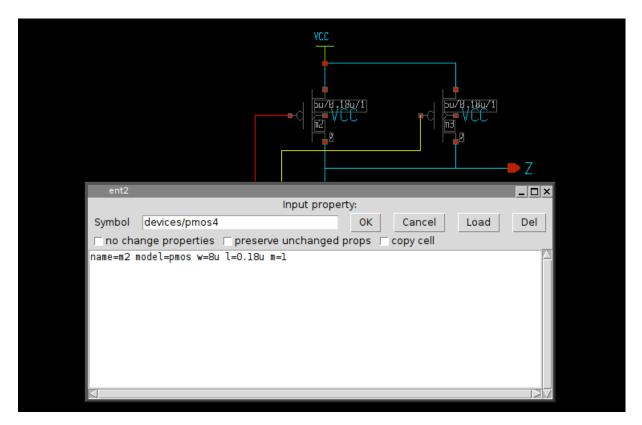

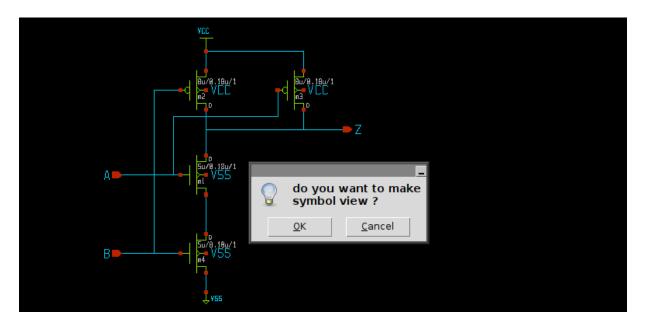

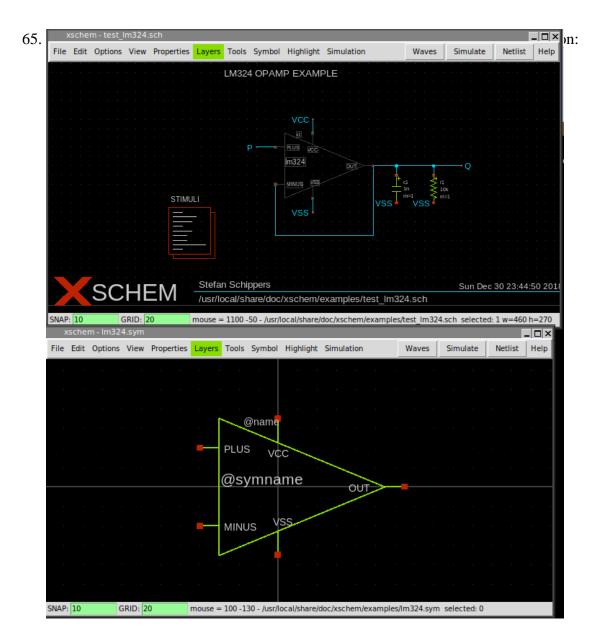

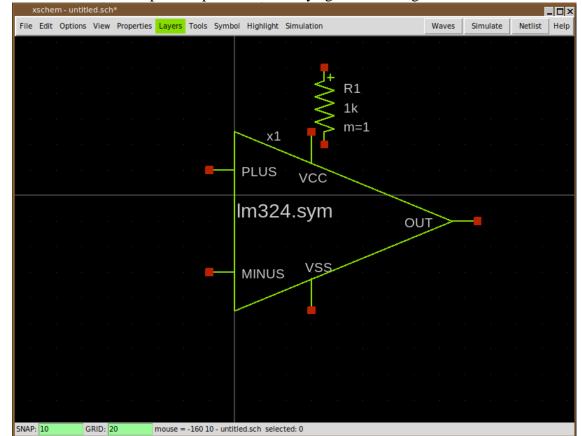

| CREATING A CIRCUIT SCHEMATIC                        | 63 |

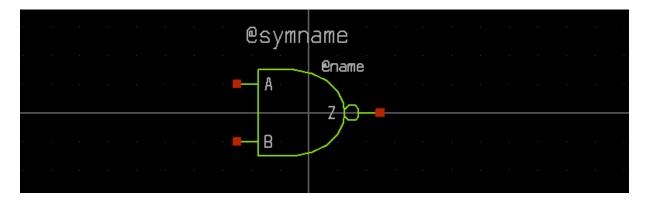

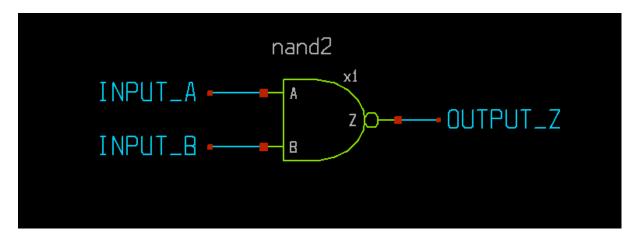

| Automatic symbol creation                           | 67 |

| Automatic Component Wiring                          | 71 |

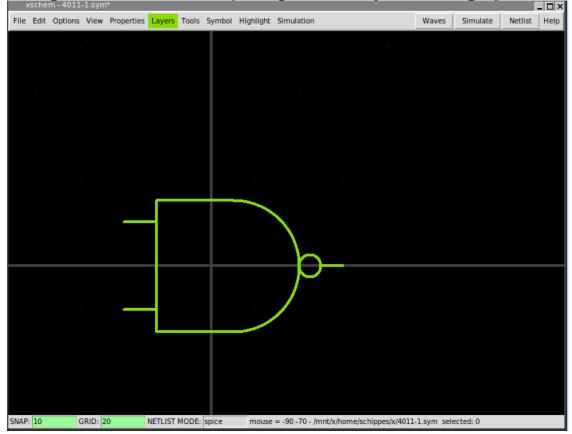

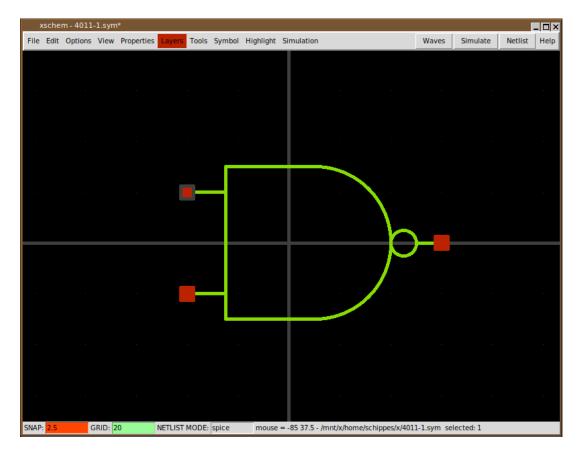

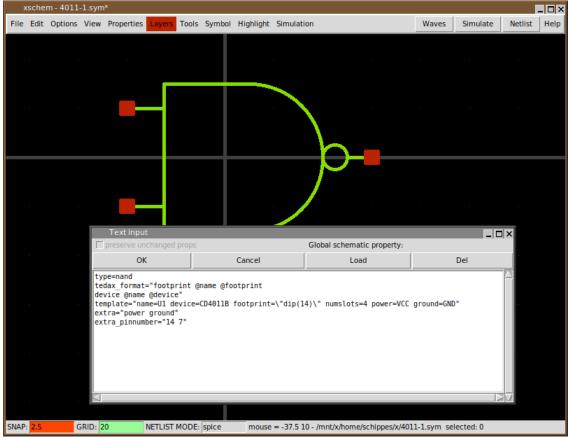

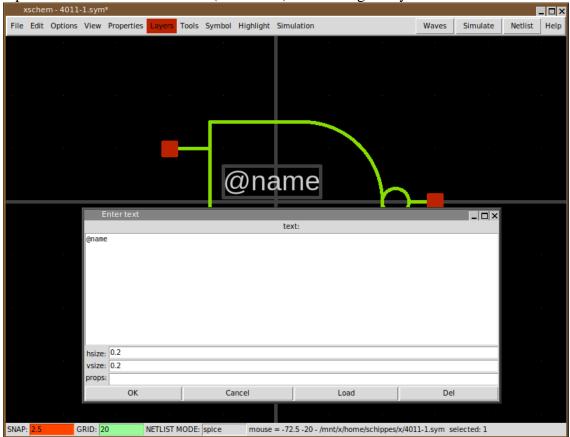

| CREATING SYMBOLS                                    | 73 |

| creating a new symbol and schematic by cloning      | 73 |

| COMPONENT PARAMETERS                                | 74 |

| EDITOR COMMANDS                                     | 78 |

| EDITOR COMMAND CHEATSHEET                           | 78 |

| KEYBIND CUSTOMIZATION                               | 81 |

| STRETCH OPERATIONS                                  | 81 |

| PLACE WIRES SNAPPING TO CLOSEST PIN OT NET ENDPOINT | 83 |

| CONSTRAINED MOVE                                    | 83 |

| NETLISTING                                          | 86 |

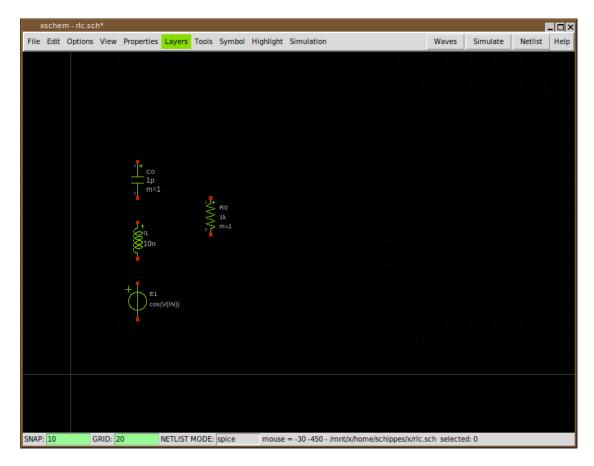

| EXAMPLE                                             | 86 |

| Other netlist formats                               |    |

| NET PROBES                                          | 89 |

| SIMULATION                                          | 95 |

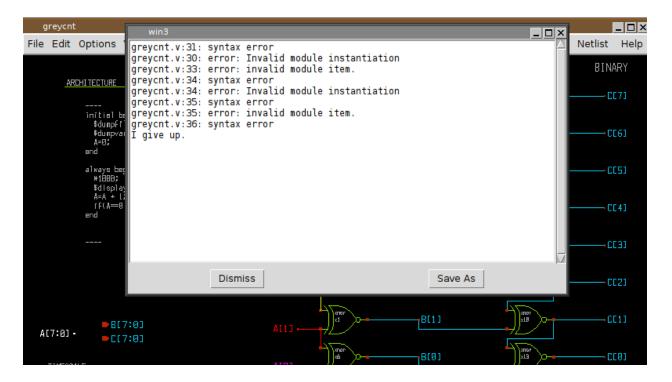

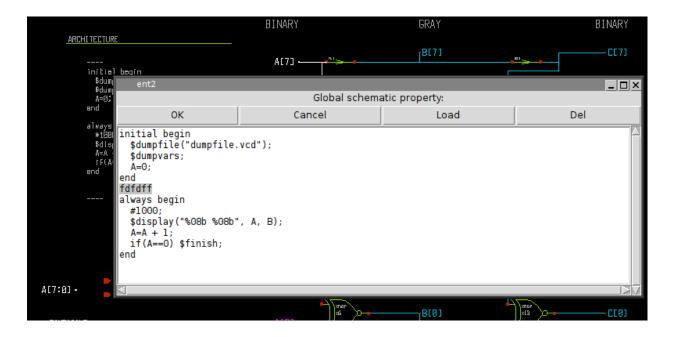

| VERILOG SIMULATION                                  | 95 |

| DEVELOPER INFO                                      |    |

| GENERAL INFORMATION                                 |    |

| SYMBOLS                                             |    |

| WIRES                                               |    |

| PROPERTIES                                          |    |

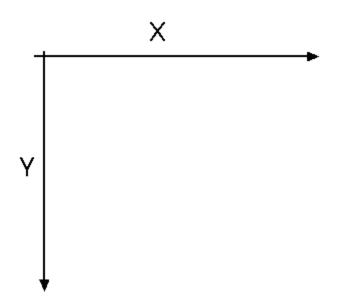

| COORDINATE SYSTEM                                   |    |

| XSCHEM FILE FORMAT SPECIFICATION                    |    |

| VERSION STRING                                                                                          |     |

|---------------------------------------------------------------------------------------------------------|-----|

| GLOBAL SCHEMATIC/SYMBOL PROPERTIES                                                                      |     |

| TEXT OBJECT                                                                                             |     |

| WIRE OBJECT                                                                                             |     |

| LINE OBJECT                                                                                             |     |

| RECTANGLE OBJECT                                                                                        |     |

| OPEN / CLOSED POLYGON OBJECT                                                                            |     |

| ARC OBJECT                                                                                              |     |

| COMPONENT INSTANCE                                                                                      |     |

| EXAMPLE OF A COMPLETE SYMBOL FILE (7805.sym)                                                            |     |

| EXAMPLE OF A COMPLETE SCHEMATIC FILE (pcb_test1.sch)                                                    |     |

| XSCHEM REMOTE INTERFACE SPECIFICATION                                                                   |     |

| GENERAL INFORMATIONS                                                                                    |     |

| TUTORIAL: INSTALL XSCHEM                                                                                |     |

| This concludes the tutorial, if all the steps were successful there is a good probabi                   | ·   |

| xschem is correctly installed on your system.                                                           |     |

| TUTORIAL: RUN A SIMULATION WITH XSCHEM                                                                  |     |

| TUTORIAL: CREATE AN XSCHEM SYMBOL                                                                       |     |

| TUTORIAL: Manage XSCHEM design / symbol libraries                                                       |     |

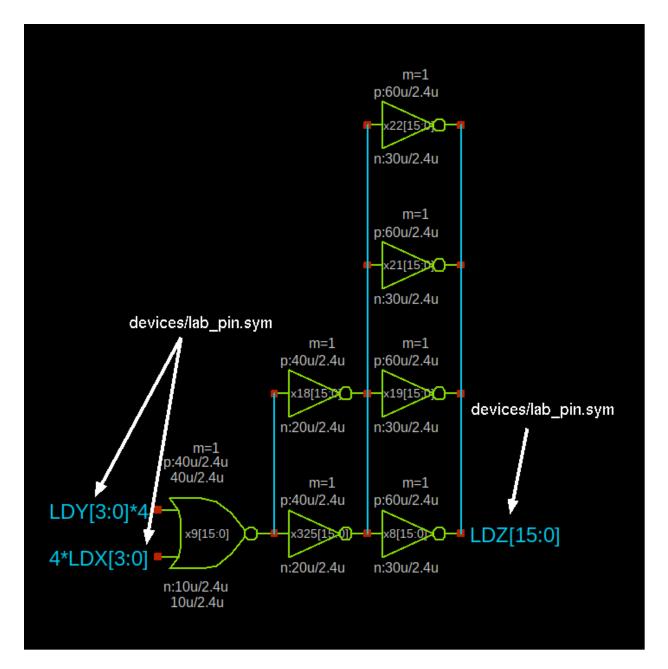

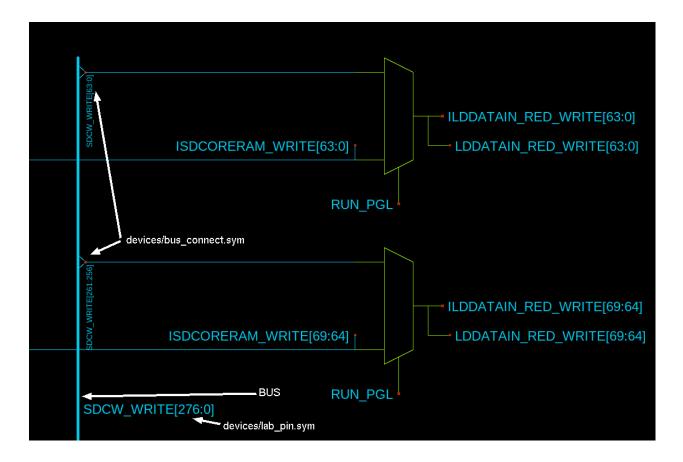

| TUTORIAL: Use Bus/Vector notation for signal bundles / arrays of instances                              |     |

| FAQ                                                                                                     |     |

| When placing a new component i want a dialog showing the defined libraries before the TCL file selector | 1 0 |

| I want new instances to get assigned a new unique name automatically                                    |     |

| Why do i have to press 'm' to move a component instead of just click and drag?                          |     |

# INDEX

- 1. What is XSCHEM

- 2. Install XSCHEM

- 3. <u>Run XSCHEM</u>

- 4. XSCHEM elements

- 5. Symbols

- 6. XSCHEM properties

- 7. Component instantiation

- 8. Symbol properties syntax

- 9. <u>Component properties syntax</u>

- 10. <u>Creating a circuit schematic</u>

- 11. <u>Creating symbols</u>

- 12. <u>Component parameters</u>

- 13. <u>Editor commands</u>

- 14. <u>Netlisting</u>

- 15. <u>Net Probes</u>

- 16. <u>Simulation</u>

- 17. <u>Developer Info, XSCHEM file format specification</u>

- 18. XSCHEM remote interface specification

# TUTORIALS

- Step by step instructions: Install XSCHEM

- Run a simulation with XSCHEM

- <u>Create a symbol with XSCHEM</u>

FAQ

<u>Common questions about XSCHEM</u>

# WHAT IS XSCHEM

Electronic systems today tend to be generally very complex and a lot of work has to be done from circuit conception to the validation of the final product. One of the milestones of this process is the creation of the circuit schematic of the electronic system.

The circuit diagram has to be drawn using an interactive computer program called *schematic editor*, this is usually a very first step in the design cycle of the product. Once the schematic has been drawn on the computer, the circuit connectivity and device list (*netlist*) can be generated and sent to a circuit simulator (spice, hspice, eldo, just to mention some) for performing circuit simulation.

So, as you probably guessed, **XSCHEM** is a schematic capture program that allows to interactively enter an electronic circuit using a graphical and easy to use interface. When the schematic has been created a circuit netlist can be generated for simulation. Currently XSCHEM supports four netlist formats:

- 1. SPICE netlist

- 2. VHDL netlist

- 3. VERILOG netlist

- 4. tEDAx netlist for Printed board editing software like pcb-rnd.

XSCHEM was initially created for VLSI design, not for printed circuit board schematics (PCB), however the recently added tEDAx netlist format is used to export XSCHEM schematics to pcb-rnd or other tEDAx-aware PCB editors. The roadmap for XSCHEM development will focus more in the future to build a tight integration with <u>pcb-rnd</u> printed board editor, joining the <u>CoralEDA</u> ecosystem philosophy.

XSCHEM initial design goal was to handle Integrated Circuit (IC) design and generate netlists for Very Large Scale digital, analog or mixed mode simulations. While the user interface looks very simple, the netlisting and rendering engine in XSCHEM are designed from the ground-up to handle in the most efficient way very large designs. Also the user interaction has no bells and whistles but is the result of doing actual work on big projects in the most efficient way. This is why for example most of the work is done with bind keys, instead of using context menus or elaborate graphical actions, simply these things will slow your work if most of your schematics have 5-8 levels of hierarchy and 1000K+ transistors.

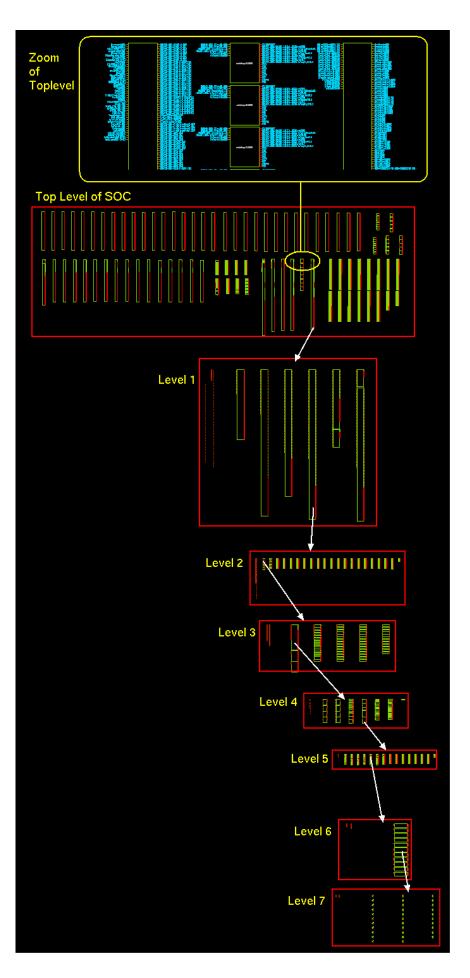

Here under a picture of a VLSI SOC (System On Chip) imported in XSCHEM. As you can see the ability of XSCHEM is to handle really big designs. This has been the primary goal during the whole development of the program. The sample design showed has more than 10 levels of hierarchy and really big schematics. For each hierarchy level one component is expanded until the leaf of the tree is reached. :-)

It is also worth to point out that XSCHEM has nothing to do with GSCHEM, the name similarity is just coincidence. <u>GSCHEM</u> is another powerful Schematic Capture program, primarily focused on board level (PCB) system design. See <u>gEDA</u> for more information.

# **INSTALL XSCHEM**

in order to install the program run the following command:

```

user:~$ cd xschem-<version>; ./configure

```

this will make all the necessary checks for required libraries and system tools. If configure ends with no errors we are ready to compile:

```

user:~$ make

```

If we want to install xschem and its required files (execute as root if you plan to do a systemwide installation, for example in /usr/local):

user:~\$ make install

This will install all the runtime needed files into the locations previously configured (can be found in Makefile.conf). To change the default installation prefix (/usr/local), please replace the configure step shown above with:

./configure --prefix=new/prefix/path

DESTDIR is supported.

For testing purposes xschem can be run and invoked from the build directory xschem-<version>/src/ without installation.

user:~\$ cd xschem-2.7.0/src && ./xschem

When xschem is running, type puts \$XSCHEM\_LIBRARY\_PATH in the xschem tcl prompt to know the library search path.

Type puts \$XSCHEM SHAREDIR to see the installation path.

Sample user design libraries are provided and installed systemwide under \${XSCHEM\_SHAREDIR/xschem\_library/. The XSCHEM\_START\_WINDOW specifies a schematic to preload at startup, to avoid absolute paths use a path that is relative to one of the XSCHEM\_LIBRARY\_PATH directories. XSCHEM will figure out the actual location. You may comment the definition if you don't want any schematic on startup. If you need to override system settings, create a ~/.xschem/xschemrc. The easiest way is to copy the system installed version from  $from \frac{\pi}{\sqrt{\pi}}/\frac{\pi}{\sqrt{\pi}}$

user:\$ mkdir ~/.xschem

user:\$ cp <install root>/share/xschem/xschemrc ~/.xschem/xschemrc

## **Detailed XSCHEM startup sequence**

- 1. If ../src/xchem.tcl with respect to current dir is existing and ../xschem\_library is also existing then we are starting from a build directory, set XSCHEM\_SHAREDIR to `pwd` and also set XSCHEM\_LIBRARY\_PATH to `pwd`/../xschem\_library.

- 2. else use compile-time (generated from configure script) provided XSCHEM\_SHAREDIR.

- 3. if in current dir there is a xschemrc file source it.

- 4. else if there is a USER\_CONF\_DIR/xschemrc file source it.

- 5. else if there is a XSCHEM\_SHAREDIR/XSChemrc file then source it XSCHEM\_SHAREDIR and USER\_CONF\_DIR are preprocessor macros passed at compile time by the configure script. The first one will be overridden only if executing from a build directory, see point 1.

- 6. if XSCHEM\_SHAREDIR not defined --> error and quit.

- 7. source \$XSCHEM\_SHAREDIR/xschem.tcl.

- 8. start loading user provided schematic file or start with empty window (or filename specified in XSCHEM\_START\_WINDOW tcl variable).

# **RUN XSCHEM**

Assuming xschem is installed in one of the \${PATH} search paths just execute:

user:~\$ xschem

the xschem window should appear. If xschem is not in the search path then specify its full pathname.

| ×             | schei | m - untitle | ed.sch  |            |         |         |              |             |           |   |  |       |          |       | _ 🗆 ×   |

|---------------|-------|-------------|---------|------------|---------|---------|--------------|-------------|-----------|---|--|-------|----------|-------|---------|

| File          | Edit  | Options     | View    | Properties | Layers  | Tools   | Symbol       | Highlight   | Simulatio | n |  | Waves | Simulate | Netli | st Help |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

| · ·           |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

|               |       |             |         |            |         |         |              |             |           |   |  |       |          |       |         |

| <b>C</b> 1112 | 10    |             |         |            |         | 110     |              |             |           |   |  |       |          |       |         |

| SNAP:         | 10    | G           | GRID: 2 | 0          | mouse = | -110 -7 | /0 - untitle | ed.sch sele | cted: 0   |   |  |       |          |       |         |

if a filename is given that file will be loaded on startup:

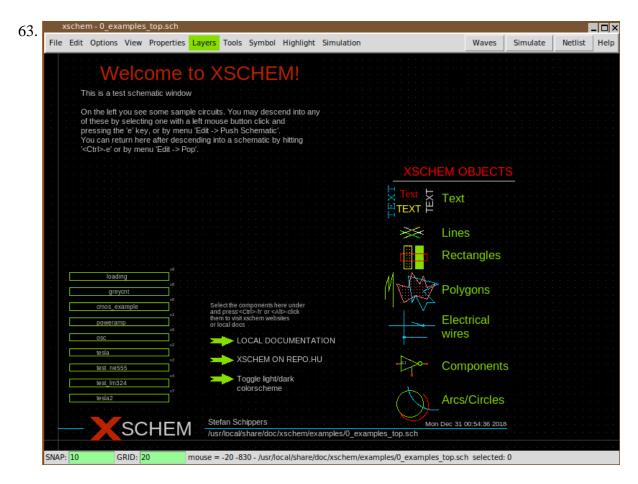

user:~\$ xschem .../xschem\_library/examples/0\_examples\_top.sch

| 1    | kscher         | n - 0_exa                            | mples                            | _top.sch                                                |                                        |                                        |                                     |                       |               |                      |                     |               |            | _ 🗆 ×   |

|------|----------------|--------------------------------------|----------------------------------|---------------------------------------------------------|----------------------------------------|----------------------------------------|-------------------------------------|-----------------------|---------------|----------------------|---------------------|---------------|------------|---------|

| File | Edit           | Options                              | View                             | Properties                                              | Layers                                 | Tools                                  | Symbol                              | Highlight             | Simulation    |                      | Waves               | Simulate      | Netlist    | Help    |

|      | : Yo           | nis is the s<br>ou may ch            | tart sc<br>ange ti               | ome<br>hematic win<br>his to any di<br>low. Just se     | dow spec<br>fferent sc                 | ified in<br>hematic                    | your .xsch<br>file or eve           | hem file.<br>en start | riable:       |                      |                     |               |            |         |

|      |                | et XSCH                              | EM_ST                            | ART_WIND                                                | OW {myl                                | ib/0_top                               | )}                                  |                       |               |                      |                     |               |            |         |

|      | or             | , if you wa                          | ant to st                        | tart with an                                            | empty wir                              | idow:                                  |                                     |                       |               |                      |                     |               |            |         |

|      | : : <u>-</u> s | et XSCH                              | EM_ST                            | ART_WIND                                                | ow {}                                  |                                        |                                     |                       |               | XSCH                 |                     | S             |            |         |

|      | of<br>pr       | these by<br>essing the<br>ou can ret | selectir<br>e 'e' key<br>urn her | some sam<br>ng one with<br>y, or by mer<br>e after desc | a left mou<br>1u 'Edit -><br>ending in | se butte<br>Push S                     | on click ar<br>chematic             | nd · · · ·            |               |                      | Text                |               |            |         |

|      |                | uri>-e∶or                            | by mei                           | nu "Edit -> P                                           | op:                                    |                                        |                                     |                       |               |                      | Lines               |               |            |         |

|      |                |                                      |                                  |                                                         |                                        |                                        |                                     |                       |               |                      | Rectangles          |               |            |         |

|      |                | loadir<br>grey                       | cnt                              | 25 x5 x5                                                |                                        |                                        | mpónents he                         |                       |               | Matt                 | Polygons            |               |            |         |

|      |                | cmos_ex                              |                                  | x1 · · · · · · · · · · · · · · · · · · ·                | · · · and                              | d press'<0<br>m to visito<br>ocal docs | Ctrl>-h'or <a<br>(schem webs</a<br> | lt>-click<br>sites    |               |                      | Electrical<br>wires |               |            |         |

|      |                | osc<br>tesla                         |                                  | s2                                                      | · · · · <b>&gt;</b>                    |                                        |                                     |                       |               |                      |                     |               |            |         |

|      |                | test ne58                            | 55                               | x3 .                                                    |                                        | 2.2.2                                  |                                     | N REPO.H              | <b>)</b>      |                      | Component           | S C C C C     |            |         |

|      |                | test lm32<br>tesla2                  | 24                               | x7                                                      | · · · · ·                              |                                        | oggle light/<br>lorschem            |                       |               |                      | Arcs/Circles        | 3             |            |         |

|      |                |                                      | 90                               | HEN                                                     | /1                                     | fan Sch                                |                                     |                       |               |                      | Dec 26 01:32:24 201 |               |            |         |

|      |                |                                      | SC                               |                                                         | ′∎ · · /mr                             | 1t/x/hon                               | ne/schippe                          | es/xschem-            | repo/trunk/xs | chem_library/example | es/0_examples_to    | p.sch         |            |         |

| SNAP | : 10           | G                                    | RID: 2                           | 0                                                       | mouse =                                | 10 -63                                 | 0 - /mnt/x                          | /home/schi            | opes/xschem   | repo/trunk/xschem    | library/examples/   | ) examples to | p.sch sele | cted: 0 |

### **XSCHEM COMMAND LINE OPTIONS**

xschem accepts short (-h) or long (--help) options:

| usage | : xschem [options | ] [schematic   symbol ]                              |

|-------|-------------------|------------------------------------------------------|

| Optio | ns:               |                                                      |

| -h    | help              | print this help                                      |

| -n    | netlist           | do a netlist of the given schematic cell             |

| -v    | version           | print version information and exit.                  |

| -V    | vhdl              | set netlist type to VHDL                             |

| -S    | simulate          | run a simulation of the current schematc file        |

|       |                   | (spice/Verilog/VHDL, depending on the netlist        |

|       |                   | type chosen).                                        |

| -w    | verilog           | set netlist type to Verilog                          |

| -i    | no rcload         | do not load any xschemrc file                        |

| -0    | netlist path      | set output for netlist                               |

| -t    | tedax _           | set netlist type to tEDAx                            |

| -s    | spice             | set netlist type to SPICE                            |

| -3    | a3page            | set page size for pdf export to A3                   |

| -x    | no x              | dont use X (only command mode)                       |

|       | events            | Do not use tclreadline, empty tcl shell prompt, dump |

|                        | activity on stdout for remote controlling other                            |

|------------------------|----------------------------------------------------------------------------|

| software               |                                                                            |

| -zrainbow              | use a raibow-looking layer color table                                     |

| -Wwaves                | show simulation waveforms                                                  |

| -fflat netlist         | set flat netlist (for spice format only)                                   |

| -rno readline          | start without the tclreadline package ( this is                            |

| —                      | necessary if stdin and stdout are to be redirected                         |

|                        | for example to /dev/null).                                                 |

| -ccolor ps             | set color postscript                                                       |

| plotfile <file></file> | use <file> as output for plot (png, svg, ps)</file>                        |

| rcfile <file></file>   | use <file> as a rc file for startup instead of the</file>                  |

|                        | default xschemrc.                                                          |

| -ppostscript           |                                                                            |

| pdf                    | export pdf schematic                                                       |

| png                    | export png schematic                                                       |

| svg                    | export svg schematic                                                       |

| -qquit                 | quit after doing things (no interactive mode)                              |

| -l <file></file>       |                                                                            |

| log <file></file>      | set a log file                                                             |

| -d <n></n>             |                                                                            |

| debug <n></n>          | set debug level: 1, 2, 3, C program debug<br>-1, -2, -3 TCL frontend debug |

| xschem: interactive so | chematic capture program                                                   |

|                        |                                                                            |

Example: xschem counter.sch the schematic file `counter.sch' will be loaded.

### **CREATING A NEW SCHEMATIC**

To create a new schematic run xschem and give a non existent filename: xschem aaa.sch

| xsche   | m -     |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      | _ 🗆 |

|---------|---------|------|------------|------------|-----------|---------|-----------|-------|-------|------|--|--|--|-----|----|----|-------|---|-----|------|-----|

| le Edit | Options | View | Properties | Layers     | Tools     | Symbol  | Highlight | : Sir | mulat | tion |  |  |  | Wav | es | Si | mulat | e | Net | list | He  |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            | Alert      |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      | Unat       | ble to ope | n file: t | est.sch |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            | 0          | к         |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

|         |         |      |            |            |           |         |           |       |       |      |  |  |  |     |    |    |       |   |     |      |     |

You can save the schematic by pressing '<ctrl shift>s' or by using the menu File - Save As:

|      |      | m - test.s |         | Properties | Lavers          | Tools  | Symbol    | Highlight      | Simulation                         | Waves           | 6     | imulate  | Netlist | - 🗆<br>Hel |

|------|------|------------|---------|------------|-----------------|--------|-----------|----------------|------------------------------------|-----------------|-------|----------|---------|------------|

| i ne | Luit | options    | VIEW    | ropences   | Layers          | TOOIS  | Symbol    | mynnync        | Simulation                         | waves           |       | innulate | Netlist |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            | Save            | file   |           |                |                                    | _               |       |          |         |            |

|      |      |            |         |            | Director        |        |           |                | l.                                 |                 |       |          |         |            |

|      |      |            |         |            | Directory       | /: /n  | nnt/x/nom | ne/schippes    | /x                                 | •               |       |          |         |            |

|      |      |            |         |            | rlc.s           | ch     |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            | 4               |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            | File <u>n</u> a | me: te | est.sch   |                |                                    | Save            |       |          |         |            |

|      |      |            |         |            | Files of t      | ype:   | Schemat   | ic files (*.se | ch) 🗆 🔤                            | Cancel          |       |          |         |            |

|      |      |            |         |            |                 | _      |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      |      |            |         |            |                 |        |           |                |                                    |                 |       |          |         |            |

|      | : 10 |            | GRID: 2 | 0          | NETLIST I       | MODE   | spice     | mouse          | = -100 -110 - /mnt/x/home/schippes | /v/test sch sel | octod | 0        |         |            |

If no filename change is needed you can just use File - Save. Now a new empty schematic file is created. You can use this test.sch for testing while reading the manual. After exiting XSCHEM you can load directly this schematic with the following commands, they are all equivalent.

```

# xschem defaults its search to the

# XSCHEM_LIBRARY_PATH root path

# .sch may be omitted, it is added by default ...

xschem test

# or ...

xschem /home/schippes/x/test.sch

# or ...

xschem ${HOME}/schippes/x/test

```

you can load test.sch when xschem is running by using the load command '<ctrl>o' key or by menu Open command. Use the file selector dialog to locate the schematic and load it in. When loading a new file XSCHEM asks to save the currently loaded schematic if it has been modified.

# **XSCHEM ELEMENTS**

### WIRES

Wires in XSCHEM are the equivalent of copper traces in printed circuit boards or electrical conductors. Wires are drawn as lines but the electrical connectivity graph is built by XSCHEM. To draw a wire segment point the mouse somewhere in the drawing window and press the 'w' key. A rubber wire is shown with one end following the mouse. Clicking the left mouse button finishes the placement. The following picture shows a set of connected wires. There are many wire segments but only 3 electrical nodes. XSCHEM recognizes connection of wires and uses this information to build up the circuit connectivity. All wires are drawn on the 'wire' layer. One electrical node in the picture below has been highlighted in red (this is a XSCHEM function we will cover later on).

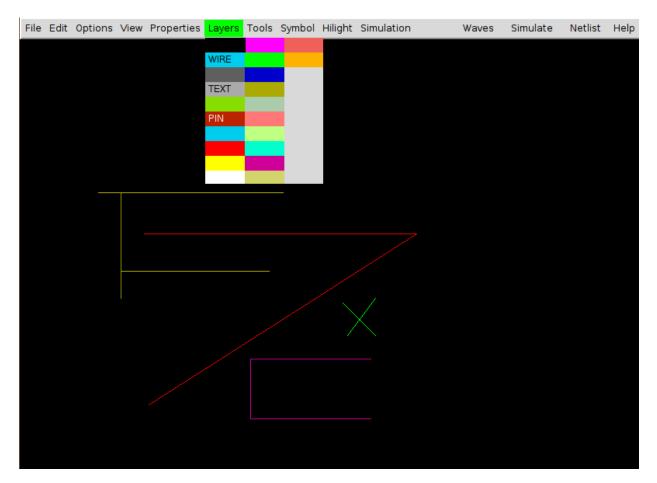

#### LINES

Lines are just segments that are used for drawing. Lines do not have any electrical meaning, in fact when building the circuit netlist, lines are completely ignored. XSCHEM uses different layers to draw lines. Each layer has its own color, allowing to draw with different colors. Lines

are placed like wires, but using the 'l' key. The 'Layers' menu allows to select various different layers (colors) for the line.

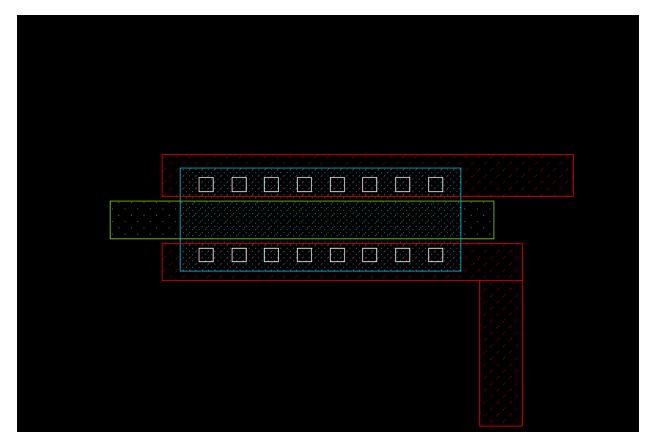

### RECTANGLES

Rectangles like Lines are drawable on multiple layers, and also do not carry any electrical information. A specific 'PIN' layer is used to make pins that are used to interconnect wires and components. Different fill styles (or no fill) can be defined for each layer. Rectangles are placed with the 'r' bindkey

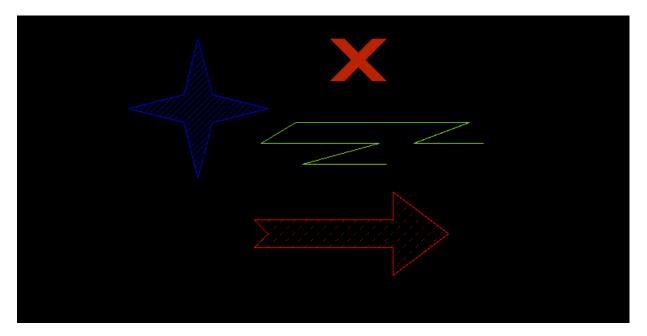

### POLYGONS

Polygons are paths that can be drawn on any layer. Placements begins with the 'ctrl-w' key and continues as long as the user clicks points on the drawing area. Placement ends when:

- the last point is coincident to the first point.

- or by clicking the right mouse button, for an open polygon.

- or by hitting the Return key, for a closed polygon (this can be done also by clicking the last point coincident to the first polygon point).

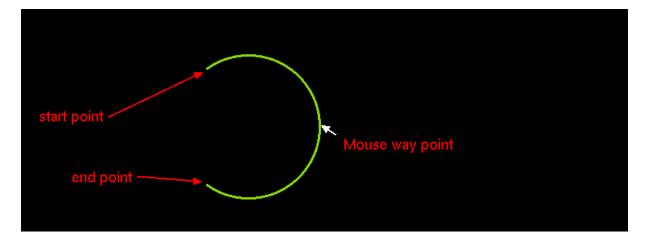

### **CIRCLES / ARCS**

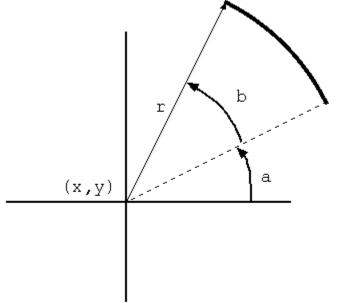

Arcs may be placed by hitting the Shift-C key. First click the start point, then the end point. Moving the mouse will show the arc passing thru the 2 points and the mouse waypoint. Clicking will place the arc. Arcs may be modified after creation by selecting in stretch mode ( Ctrl-Buttonl-drag ) one of the arc ends or the arc center:

- (end point selected in stretch mode): by starting a move (m) operation and moving the mouse the arc sweep may be changed.

- (start point selected in stretch mode):by starting a move (m) operation and moving the mouse the start arc angle may be changed.

- (arch center selected in stretch mode): by starting a move (m) operation and moving the mouse the arc radius may be changed.

If a circle is needed then use the Ctrl-Shift-C key combination.

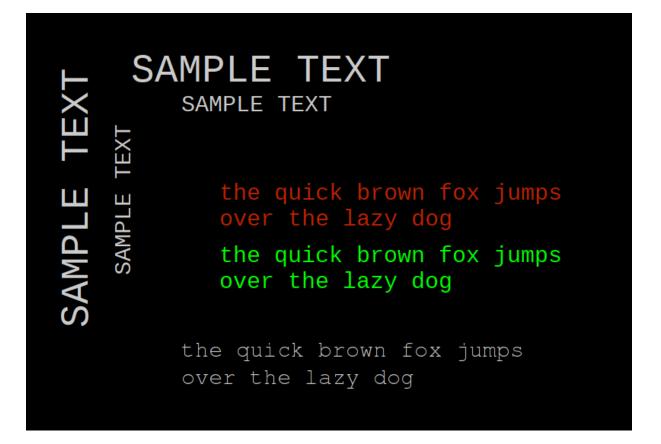

TEXT

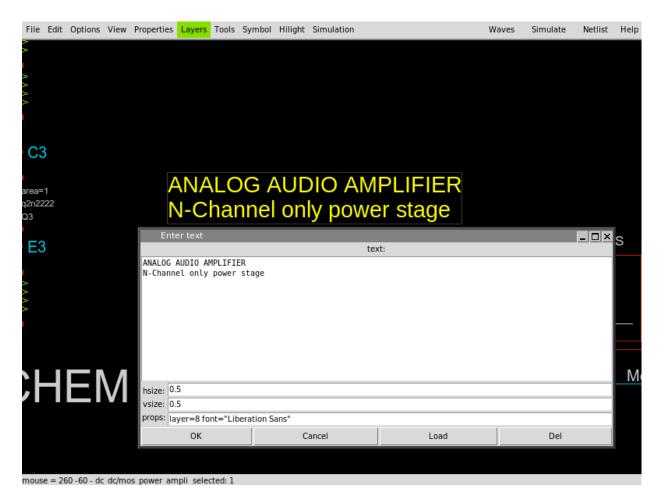

Text can be placed with the 't' bindkey. A dialog box appears where the user inputs the text and text size.

The layer property can be used to draw text on a different layer, for example, setting layer=6 will draw on cyan color. A font property is defined to change the default font. Use only Monospaced fonts because bounding box is not correctly calculated by XSCHEM for proportional typefaces. You will learn in the <u>xschem properties chapter</u> how to set, edit and change object properties.

| Def                                                | ault      | text   |      |

|----------------------------------------------------|-----------|--------|------|

| Dif                                                | feren     | t laye | er   |

| and                                                | d diff    | erent  | font |

| Entertext<br>Different layer<br>and different font | tex       | kt:    |      |

| hsize: 2                                           |           |        |      |

| vsize: 2<br>props: laver=6 font="Nim               | hus Mono" |        |      |

| OK                                                 | Cancel    | Load   | Del  |

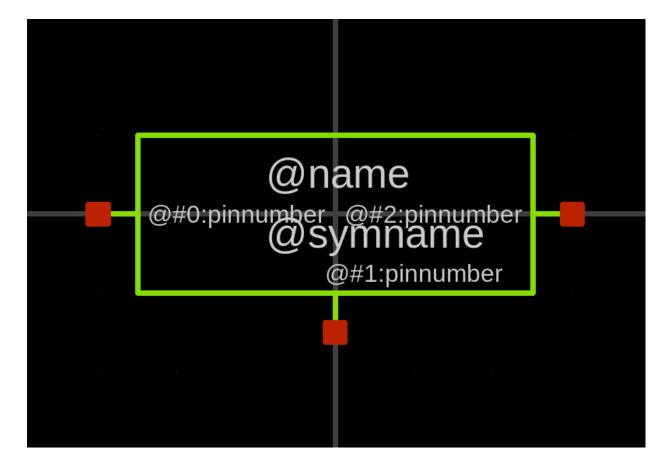

# SYMBOLS

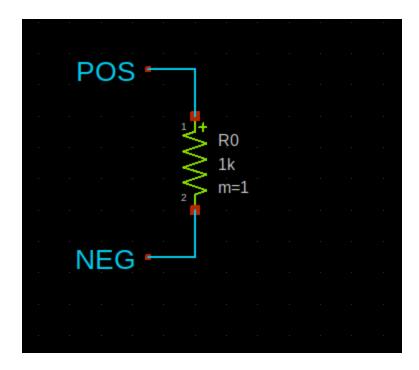

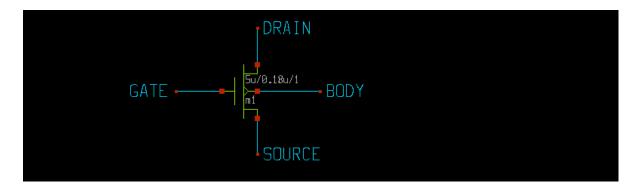

Symbols are graphical elements that represent electrical components. A symbol represents an electronic device, like for example a resistor, a bipolar transistor, an amplifier etc. As you can see graphically symbols are built with lines, rectangles, polygons and texts, the graphical primitives shown before. In the picture below some components are placed in a schematic window. Components are instances of symbols. For example you see three placements of the 'npn' bipolar transistor symbol. Like in C++, where objects are instances of classes, here components are instances of symbols.

Symbols (like schematic drawings) are stored in xschem libraries. For XSCHEM a library is just a directory placed under the XSCHEM\_LIBRARY\_PATH directory, see the <u>installation slide</u>. A symbol is stored in a .sym file.

```

user:~$ cd .../share/xschem/xschem_library/

user:xschem_library$ ls

devices

user:xschem_library$ cd devices

user:devices$ ls *.sym

ammeter.sym generic.sym noconn.sym

switch_hsp.sym

```

| arch_declarations.sym<br>switch.sym                                                             | gnd.sym                               | npn.sym                                             |

|-------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------|

| architecture.sym<br>title.sym                                                                   | ind.sym                               | opin.sym                                            |

| assign.sym<br>tline hsp.sym                                                                     | iopin.sym                             | <pre>package_not_shown.sym</pre>                    |

| attributes.sym<br>use.sym                                                                       | ipin.sym                              | package.sym                                         |

| <pre>bus_connect_not_shown.sym vccs.sym</pre>                                                   | isource_arith.sym                     | param_agauss.sym                                    |

| bus_connect.sym<br>vcr.sym                                                                      | isource_pwl.sym                       | param.sym                                           |

| capa.sym<br>vcvs.sym                                                                            | isource.sym                           | parax_cap.sym                                       |

| cccs.sym<br>vdd.sym                                                                             | k.sym                                 | pmos3.sym                                           |

| ccvs.sym<br>verilog_delay.sym                                                                   | lab_pin.sym                           | pmos4.sym                                           |

| connect.sym<br>verilog timescale.sym                                                            | lab_wire.sym                          | pmosnat.sym                                         |

| delay_hsp.sym<br>vsource arith.sym                                                              | launcher.sym                          | pnp.sym                                             |

| delay_line.sym<br>vsource pwl.sym                                                               | <pre>netlist_at_end.sym</pre>         | port_attributes.sym                                 |

| delay.sym<br>vsource.sym                                                                        | <pre>netlist_not_shown.sym</pre>      | res.sym                                             |

| diode.sym<br>zener.sym                                                                          | netlist.sym                           | spice_probe.sym                                     |

| <pre>flash_cell.sym generic_pin.sym user:devices\$ cdshare/ user:xschem\$ ls examples pcb</pre> | nmos3.sym<br>nmos4.sym<br>doc/xschem/ | <pre>spice_probe_vdiff.sym switch_hsp_pwl.sym</pre> |

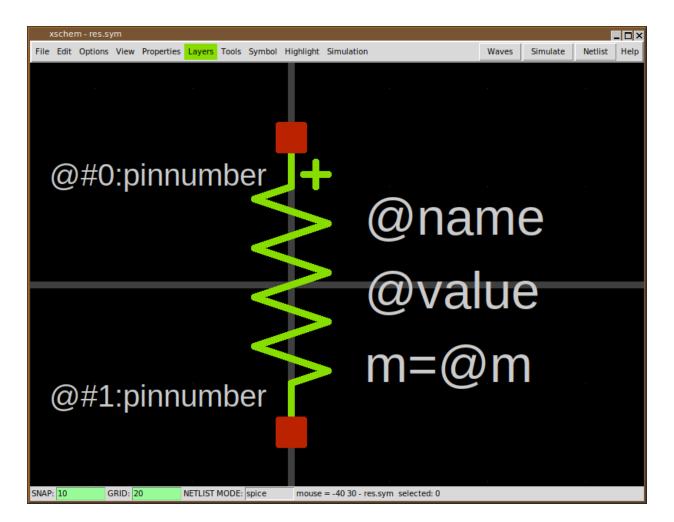

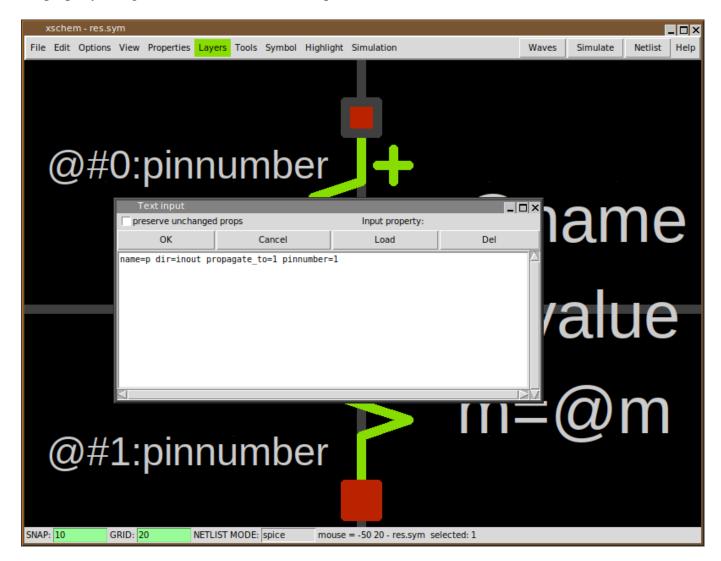

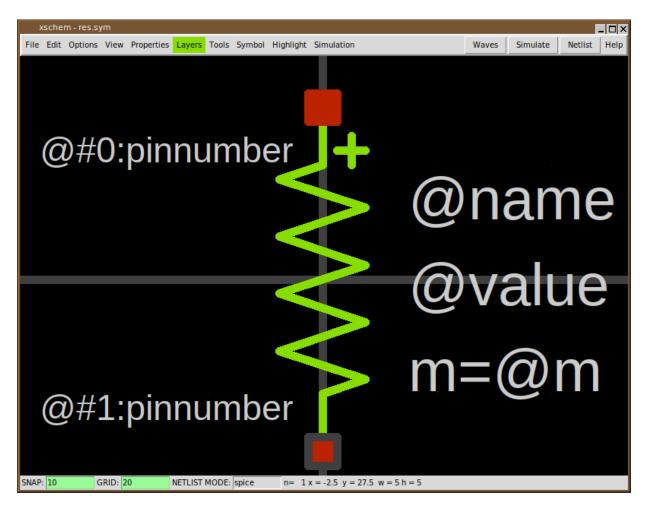

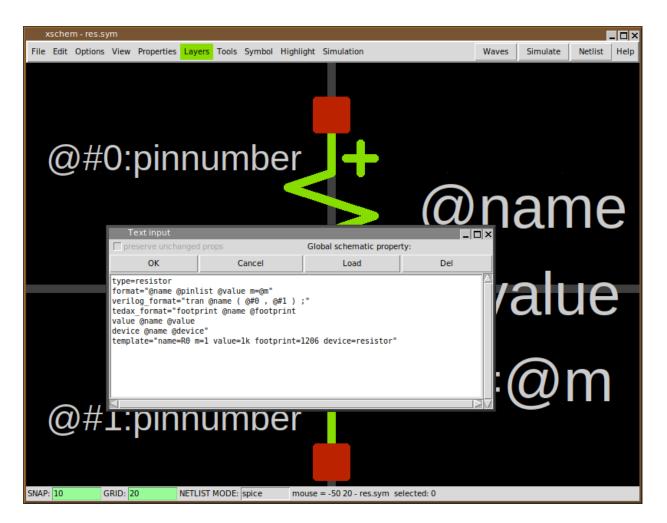

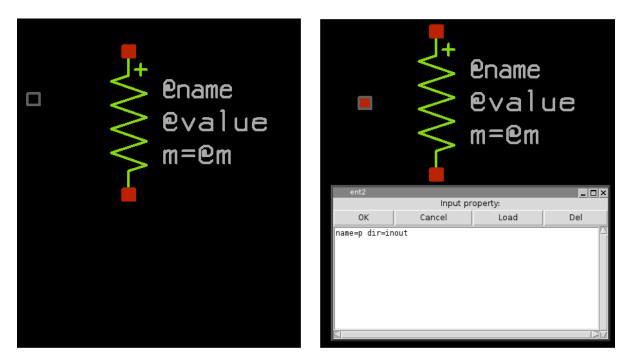

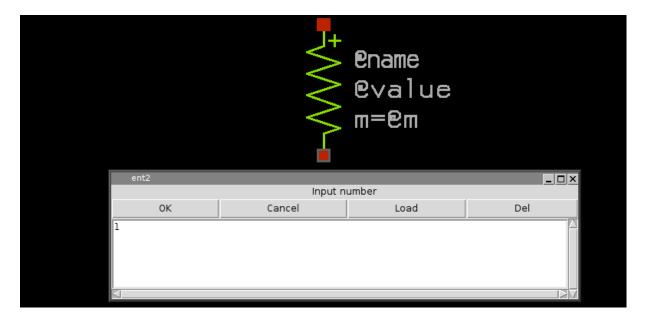

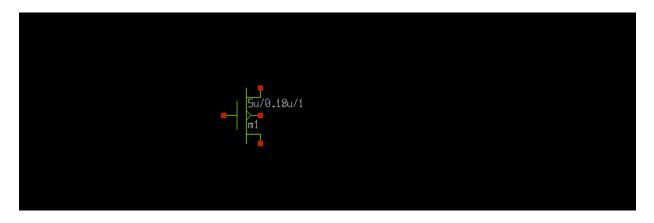

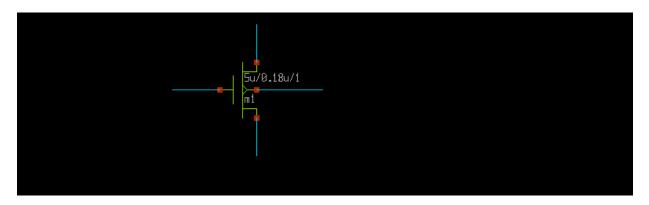

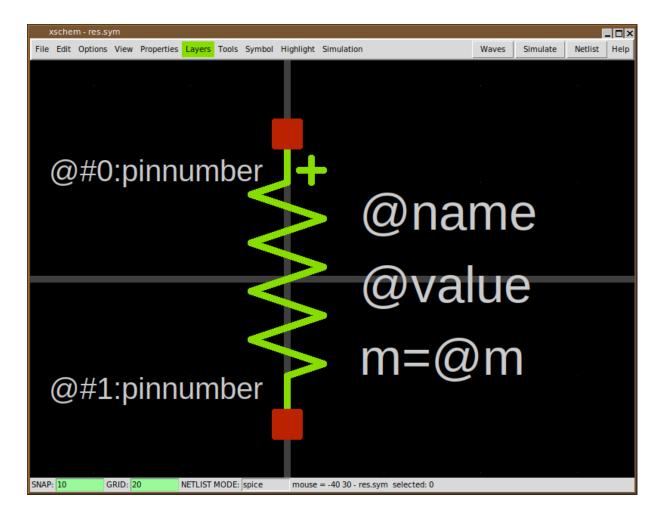

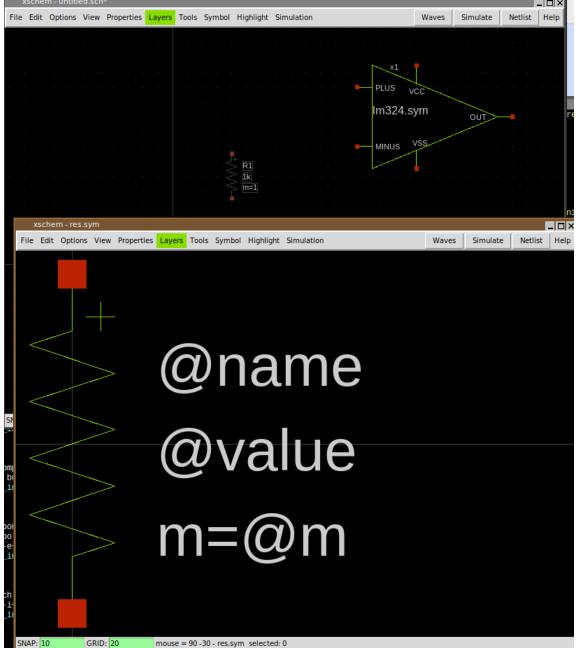

To place a symbol in the schematic window press the 'Insert' key. A file chooser pops up, go to the xschem devices directory (.../share/xschem/xschem\_library/devices in the distribution by default) and select a symbol (res.sym for example). The selected symbol will be instantiated as a component in the schematic at the mouse pointer coordinates.

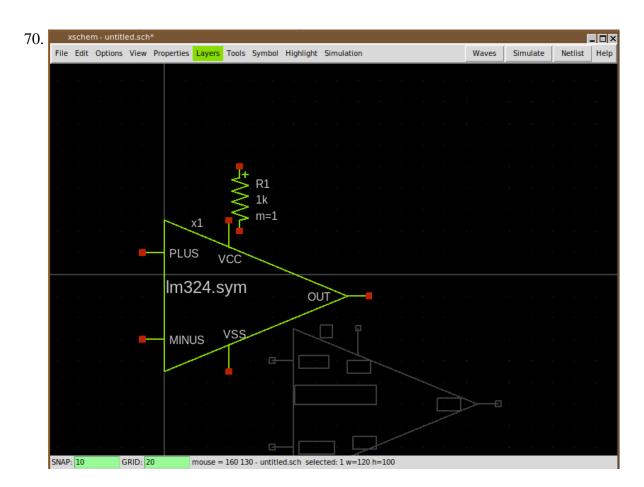

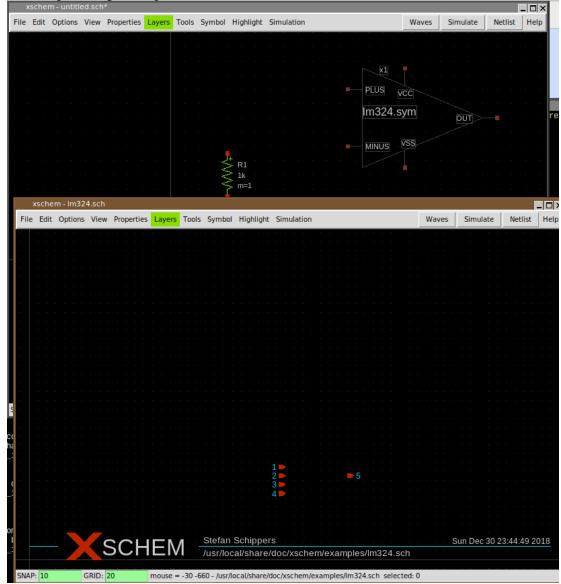

The best way to understand how a symbol is defined is to analyze an existing one. Load a test schematic (for example test.sch). Let's consider the resistor symbol. Use the Insert key to place the devices/res.sym symbol.

| x    | scher | n - test.s | ich*    |            |                    |       |                                               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |          |         | _ 🗆 × |

|------|-------|------------|---------|------------|--------------------|-------|-----------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------|---------|-------|

| File | Edit  | Options    | View    | Properties | Layers             | Tools | Symbol                                        | Highlight  | Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Waves                 | Simulate | Netlist | Help  |

|      |       |            |         |            |                    |       |                                               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |          |         |       |

|      |       |            |         |            |                    |       |                                               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |          |         |       |

|      |       |            |         |            | Choose             | symbo |                                               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                     |          |         |       |

|      |       |            |         | Dire       | ectory:            | _     | /home/so                                      | hippes/sha | re/xschem/xschem_library/devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | - 🕅                   |          |         |       |

|      |       |            |         | own        | n.sym              | pr    | nos3.sym<br>nos3.sym<br>nos4.sym<br>noshv4.sy | I          | <pre>por_attributes.sym por_attributes.sym por_attr</pre> | title<br>tilin<br>use |          |         |       |

|      |       |            |         | ym         |                    | _     | nosnat.sy<br>1p.sym                           | 'n         | switch.sym                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | vcc<br>vcr            |          |         |       |

|      |       |            |         |            | ile <u>n</u> ame   | -     |                                               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ▶<br>Open             |          |         |       |

|      |       |            |         | File       | s of <u>t</u> ype: | Sym   | bol files                                     | (*.sym)    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Cancel                |          |         |       |

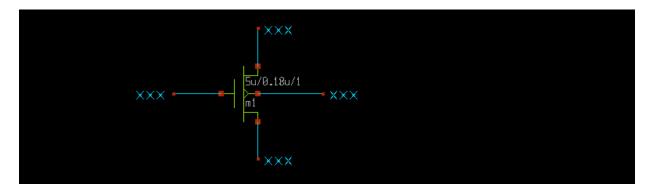

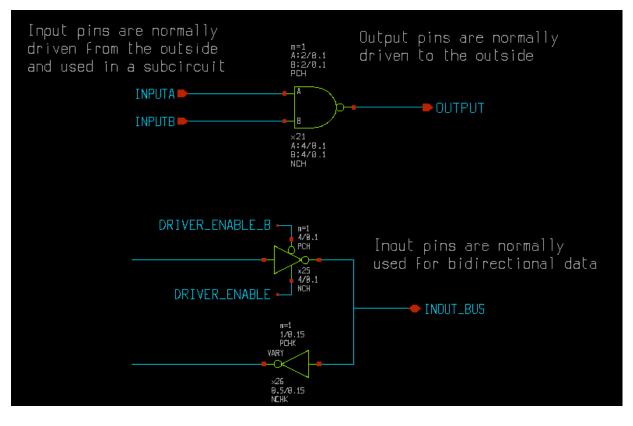

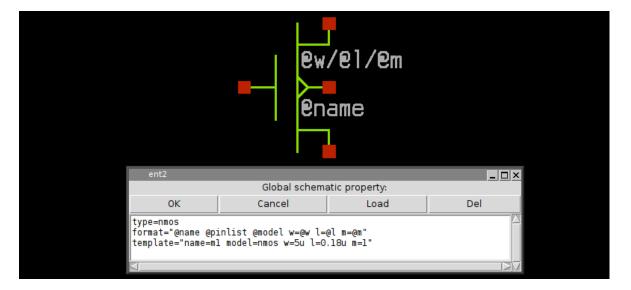

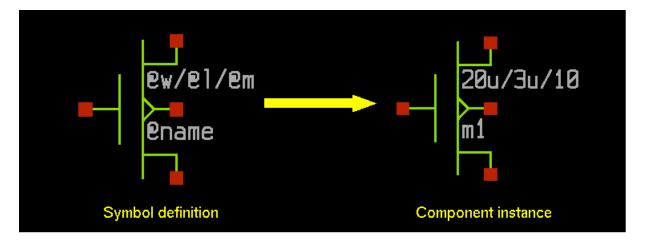

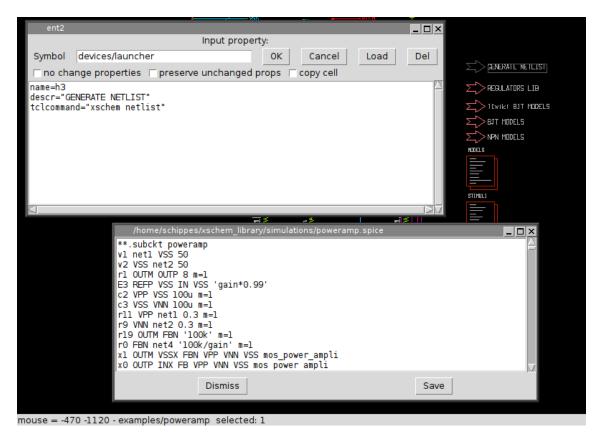

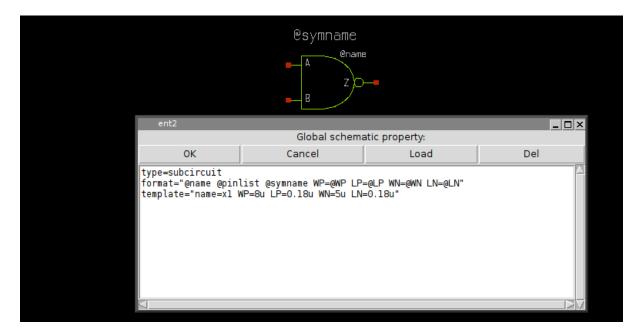

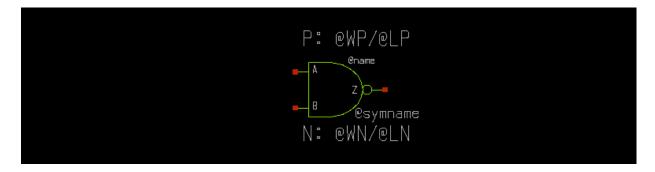

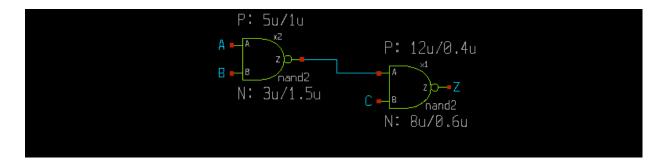

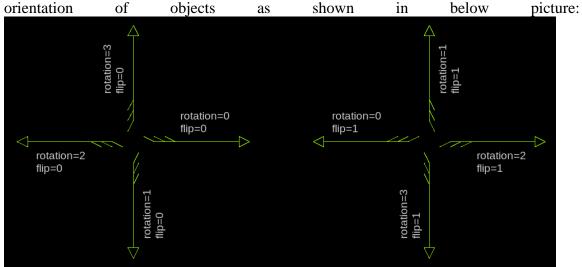

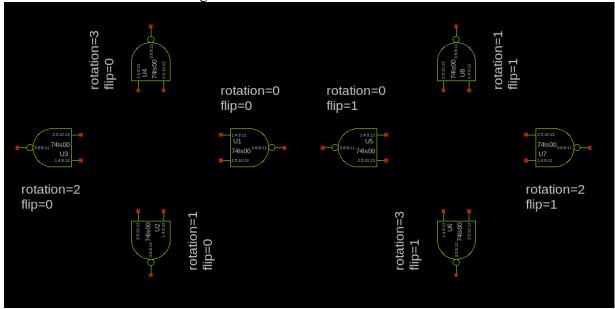

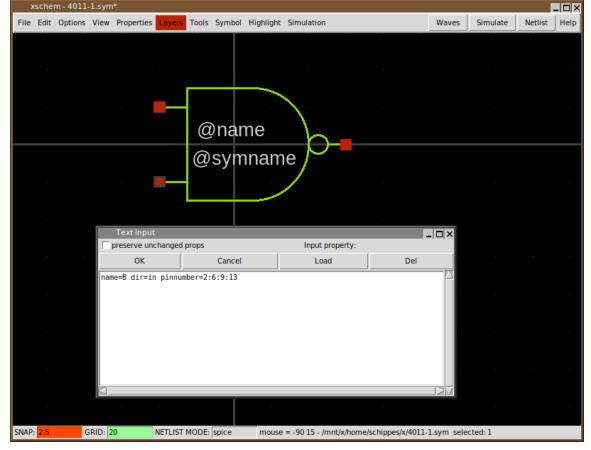

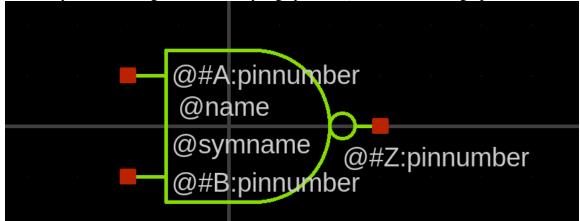

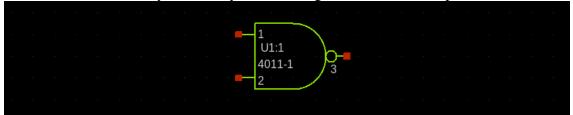

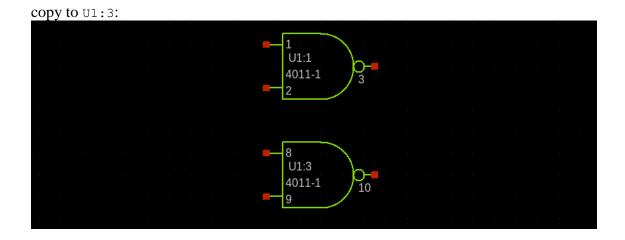

|      |       |            |         |            |                    |       |                                               |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                       |          |         |       |